## NOTES ON DIGITAL ELECTRONICS

B.Tech. II YEAR - II Sem. (2022-23)

#### MALLADI SUNDER RAO

ASSISTANT PROFESSOR

DEPARTMENT OF ELECTRICAL&ELECTRONICS ENGINEERING

NARSIMHA REDDY ENGINEERING COLLEGE

(UGC AUTONOMOUS)

Approved by AICTE, New Delhi & Affiliated to JNTUH, Hyderabad Accredited by NAAC with A Grade, Accredited by NBA

Maisammguda (V), Dhulapally (P), Medchal (M) Secunderabad-14

NARSIMHA REDDY ENGINEERING COLLEGE

#### **DIGITAL ELECTRONICS**

#### **SYLLABUS**

#### UNIT - I

**Fundamentals of Digital Systems and Logic Families:** Digital signals, digital circuits, AND, OR, NOT, NAND, NOR and Exclusive-OR operations, Boolean algebra, examples of IC gates, number systems binary, signed binary, octal hexadecimal number, binary codes, characteristics of digital ICs, digital logic families, TTL, Schottky TTL and CMOS logic, interfacing CMOS and TTL, Tri-state logic.

#### UNIT - II

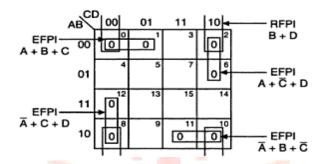

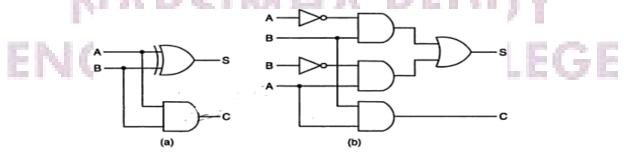

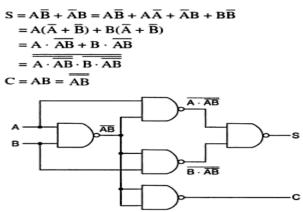

Combinational Digital Circuits: Standard representation for logic functions, K-map representation, and simplification of logic functions using K-map, minimization of logical functions. care conditions, ultiplexer, De-Multiplexer/Decoders, Adders, Subtractors, BCD arithmetic, carry look ahead adder, serial ladder, ALU, elementary ALU design, popular MSI chips, digital comparator, parity hecker/generator, code converters, priority encoders, decoders/drivers for display devices, Q-M method of function realization.

#### UNIT - III

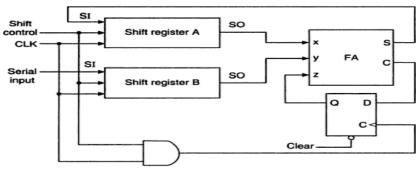

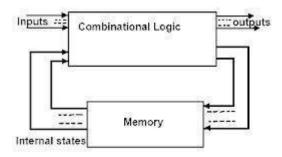

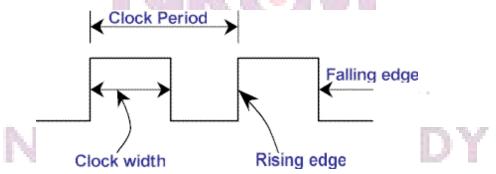

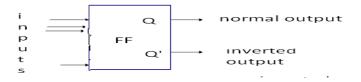

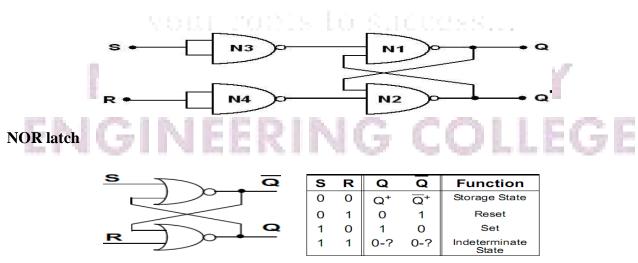

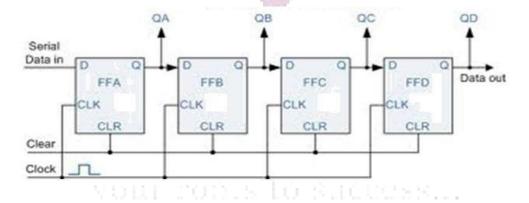

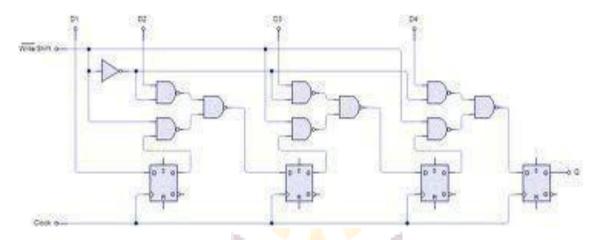

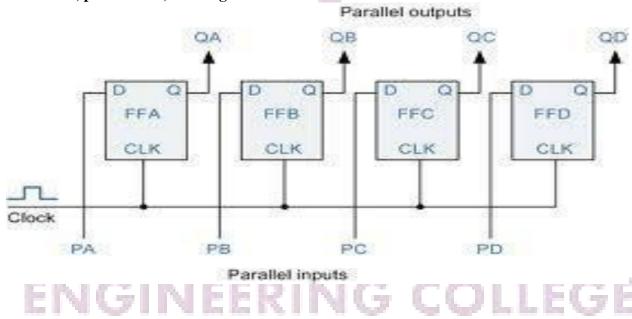

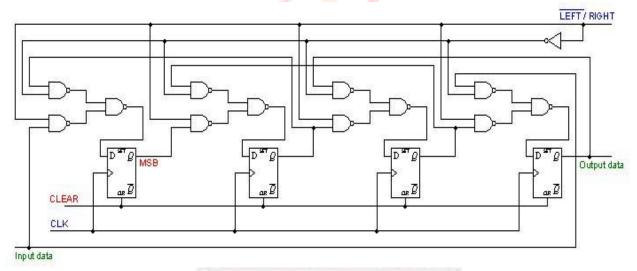

Sequential Circuits and Systems: A 1-bit memory, the circuit properties of Bi-stable latch, the clocked SR flip flop, J, K, T and D types flip-flops, applications of flip-flops, shift registers, applications of shift egisters, serial to parallel converter, parallel to serial converter, ring counter, sequence generator, ripple (Asynchronous) counters, synchronous counters, asynchronous sequential counters, applications of counters.

#### **UNIT IV**

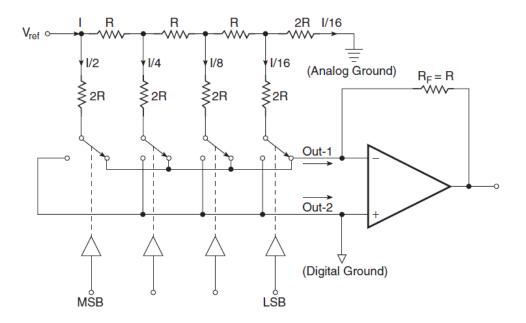

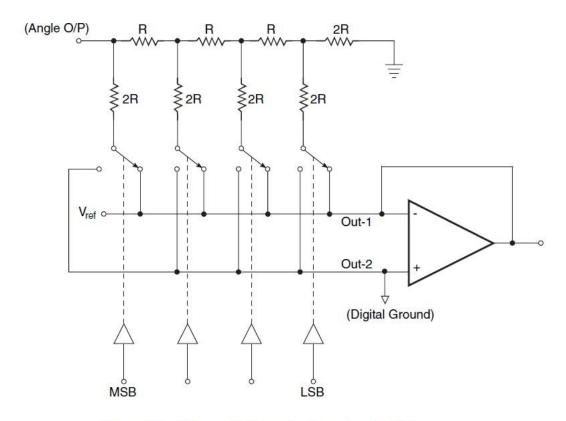

A/D and D/A Converters: Digital to analog converters: weighted resistor/converter,R-2R Ladder D/A converter, specifications for D/A converters, examples of D/A converter lCs, sample and hold circuit, analog to digital converters: quantization and encoding, parallel comparator A/D converter, successive approximation A/D converter, counting A/D converter, dual slope A/D converter, A/D converter using voltage to frequency and voltage to time conversion, specifications of A/D converters, example of A/D converter ICs.

#### UNIT - V

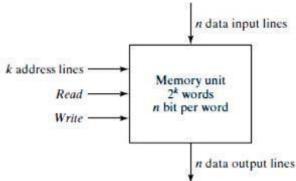

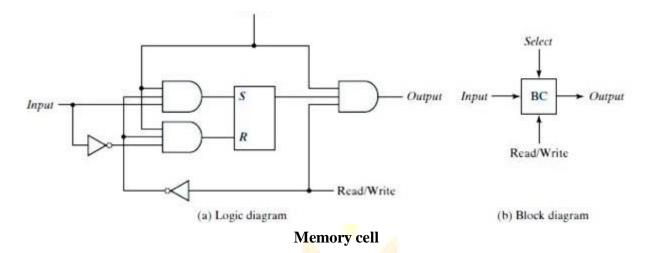

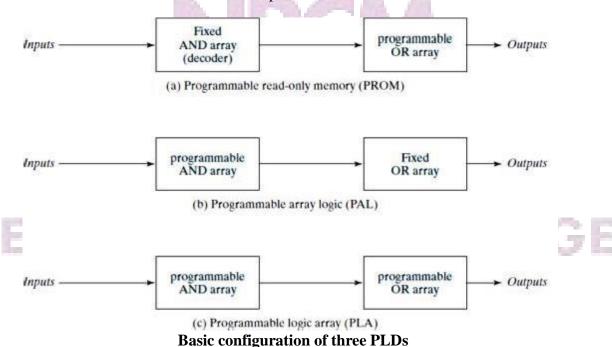

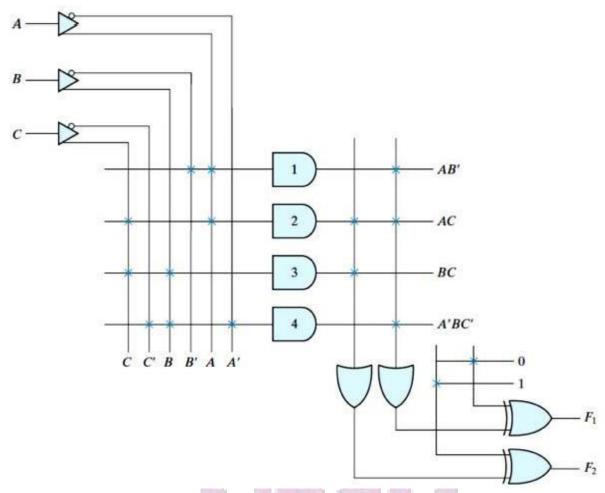

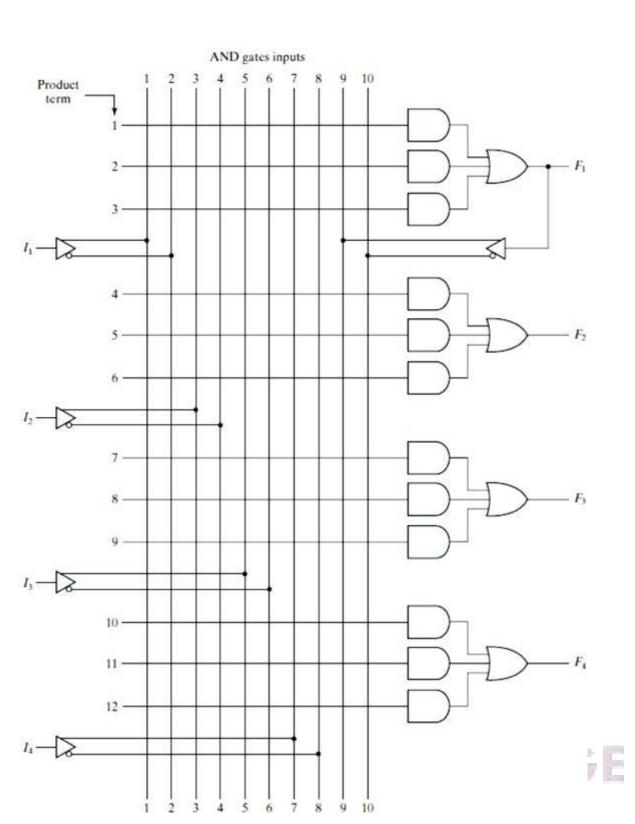

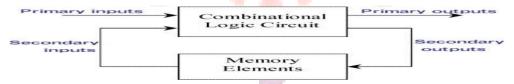

Semiconductor Memories and Programmable Logic Devices: Memory organization and operation, expanding memory size, classification and characteristics of memories, sequential memory, read only memory (ROM), read and write memory (RAM), content addressable memory (CAM), charge de coupled device memory (CCD), commonly used memory chips, ROM as a PLD, Programmable logic array, Programmable array logic, complex Programmable logic devices (CPLDS), Field Programmable Gate Array (FPGA).

ENGINEERING COLLEGE

#### **UNIT - 1**

#### Fundamentals of Digital Systems and Logic Families:

- Introduction about digital system

- Philosophy of number systems

- Complement representation of negative numbers

- Binary arithmetic

- Binary codes

- Error detecting & error correcting codes

- Hamming codes

#### INTRODUCTION ABOUT DIGITAL SYSTEM

A Digital system is an interconnection of digital modules and it is a system that manipulates discrete elements of information that is represented internally in the binary form.

Now a day's digital systems are used in wide variety of industrial and consumer products such as automated industrial machinery, pocket calculators, microprocessors, digital computers, digital watches, TV games and signal processing and so on.

#### **Characteristics of Digital systems**

- Digital systems manipulate discrete elements of information.

- Discrete elements are nothing but the digits such as 10 decimal digits or 26 letters of alphabets and so on.

- Digital systems use physical quantities called signals to represent discrete elements.

- In digital systems, the signals have two discrete values and are therefore said to be binary.

- A signal in digital system represents one binary digit called a bit. The bit has a value either 0 or 1.

#### Analog systems vs Digital systems

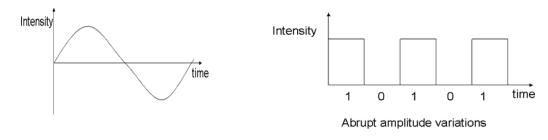

Analog system process information that varies continuously i.e; they process time varying signals that can take on any values across a continuous range of voltage, current or any physical parameter.

Digital systems use digital circuits that can process digital signals which can take either 0 or 1 for binary system.

#### Advantages of Digital system over Analog system

#### 1. Ease of programmability

The digital systems can be used for different applications by simply changing the program without additional changes in hardware.

#### 2. Reduction in cost of hardware

The cost of hardware gets reduced by use of digital components and this has been possible due to advances in IC technology. With ICs the number of components that can be placed in a given area of Silicon are increased which helps in cost reduction.

#### 3. High speed

Digital processing of data ensures high speed of operation which is possible due to advances in Digital Signal Processing.

#### 4. High Reliability

Digital systems are highly reliable one of the reasons for that is use of error correction codes.

#### 5. Design is easy

The design of digital systems which require use of Boolean algebra and other digital techniques is easier compared to analog designing.

#### 6. Result can be reproduced easily

Since the output of digital systems unlike analog systems is independent of temperature, noise, humidity and other characteristics of components the reproducibility of results is higher in digital systems than in analog systems.

### Disadvantages of Digital Systems

- Use more energy than analog circuits to accomplish the same tasks, thus producing more heat as well.

- Digital circuits are often fragile, in that if a single piece of digital data is lost or misinterpreted the meaning of large blocks of related data can completely change.

- Digital computer manipulates discrete elements of information by means of a binary code.

- Quantization error during analog signal sampling.

#### **NUMBER SYSTEM**

Number system is a basis for counting varies items. Modern computers communicate and operate with binary numbers which use only the digits 0 &1. Basic number system used by humans is Decimal number system.

For Ex: Let us consider decimal number 18. This number is represented in binary as 10010.

We observe that binary number system take more digits to represent the decimal number. For large numbers we have to deal with very large binary strings. So this fact gave rise to three new number systems.

- i) Octal number systems

- ii) Hexa Decimal number system

- iii) Binary Coded Decimal number(BCD) system

To define any number system we have to specify

- Base of the number system such as 2,8,10 or 16.

- The base decides the total number of digits available in that number system.

- First digit in the number system is always zero and last digit in the number system is always base-1.

#### **Binary number system:**

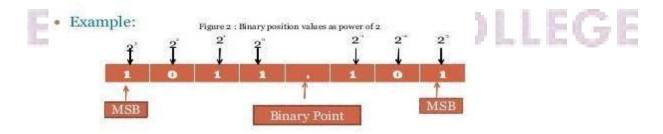

The binary number has a radix of 2. As r = 2, only two digits are needed, and these are 0 and 1. In binary system weight is expressed as power of 2.

The left most bit, which has the greatest weight is called the Most Significant Bit (MSB). And the right most bit which has the least weight is called Least Significant Bit (LSB).

For Ex:

$$1001.01_2 = [(1) \times 2^3] + [(0) \times 2^2] + [(0) \times 2^1] + [(1) \times 2^0] + [(0) \times 2^{-1}] + [(1) \times 2^2]$$

$1001.01_2 = [1 \times 8] + [0 \times 4] + [0 \times 2] + [1 \times 1] + [0 \times 0.5] + [1 \times 0.25]$

$1001.01_2 = 9.25_{10}$

#### **Decimal Number system**

The decimal system has ten symbols: 0,1,2,3,4,5,6,7,8,9. In other words, it has a base of 10.

#### **Octal Number System**

Digital systems operate only on binary numbers. Since binary numbers are often very long, two shorthand notations, octal and hexadecimal, are used for representing large binary numbers. Octal systems use a base or radix of 8. It uses first eight digits of decimal number system. Thus it has digits from 0 to 7.

#### **Hexa Decimal Number System**

The hexadecimal numbering system has a base of 16. There are 16 symbols. The decimal digits 0 to 9 are used as the first ten digits as in the decimal system, followed by the letters A, B, C, D, E and F, which represent the values 10, 11,12,13,14 and 15 respectively.

| Decima | Binar | Octal    | Hexadeci |

|--------|-------|----------|----------|

| 1      | y     | The same | mal      |

| 0      | 0000  | 0        | 0        |

| 1      | 0001  | 1        | 1        |

| 2      | 0010  | 2        | 2        |

| 3      | 0011  | 3        | 3        |

| 4      | 0100  | 4        | 4        |

| 5      | 0101  | 5        | 5        |

| 6      | 0110  | 6        | 6        |

| 7      | 0111  | 7        |          |

| 8      | 1000  | 10       | 8        |

| 9      | 1001  | 11       | 9        |

| 10     | 1010  | 12       | A        |

| 11     | 1011  | 13       | В        |

| 12     | 1100  | 14       | C        |

| 13     | 1101  | 15       | D        |

| 14     | 1110  | 16       | E        |

| 15     | 1111  | 17       | F        |

#### **Number Base conversions**

The human beings use decimal number system while computer uses binary number system. Therefore it is necessary to convert decimal number system into its equivalent binary.

- i) Binary to octal number conversion

- ii) Binary to hexa decimal number conversion

The binary number: 001 010 011 000 100 101 110 111

The octal number: 1 2 3 0 4 5 6 7

The binary number: 0001 0010 0100 1000 1001 1010 1101 1111

The hexadecimal number: 1 2 5 8 9 A D F

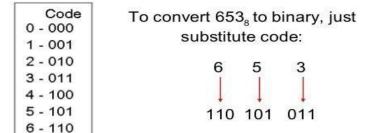

iii) Octal to binary Conversion

Each octal number converts to 3 binary digits

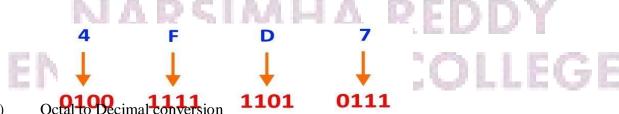

iv) Hexa to binary conversion

7 - 111

v) Octal to Decimal conversion Ex: convert 4057.06<sub>8</sub> to octal

$$= 4x8^3 + 0x8^2 + 5x8^1 + 7x8^0 + 0x8^{-1} + 6x8^{-2}$$

$$=2095.0937_{10}$$

vi) Decimal to Octal Conversion

Ex: convert 378.93<sub>10</sub> to octal

378<sub>10</sub> to octal: Successive division:

$$=572_{8}$$

0.93<sub>10</sub> to octal:

$$0.93x8=7.44$$

$$0.44x8=3.52$$

$$0.53x8=4.16$$

$$0.16x8=1.28$$

$$=0.7341_{8}$$

vii) Hexadecimal to Decimal Conversion

Ex: 5C7<sub>16</sub> to decimal

$$=(5x16^2)+(Cx16^1)+(7x16^0)$$

$$=147_{10}$$

viii) Decimal to Hexadecimal Conversion

Ex: 2598.67510

$$= A26_{(16)}$$

$$0.67510=0.675x16 -- 10.8$$

=  $0.800x16 -- 12.8$

=  $0.800x16 -- 12.8$

=  $0.800x16 -- 12.8$

=  $0.ACCC_{16}$

$$2598.675_{10} = A26.ACCC_{16}$$

#### ix) Octal to hexadecimal conversion:

The simplest way is to first convert the given octal no. to binary & then the binary no. to hexadecimal.

Ex: 756.603<sub>8</sub>

| 7    | 5    | 6    | Sec. 1 | 6    | 0    | 3    |

|------|------|------|--------|------|------|------|

| 111  | 101  | 110  | 100    | 110  | 000  | 011  |

| 0001 | 1110 | 1110 | 790    | 1100 | 0001 | 1000 |

| 1    | Е    | Е    |        | С    | 1    | 8    |

#### x) Hexadecimal to octal conversion:

First convert the given hexadecimal no. to binary & then the binary no. to octal.

Ex: B9F.AE16

| В    | 9    | F.   | since this | A        | Е    |     |     |

|------|------|------|------------|----------|------|-----|-----|

| 1011 | 1001 | 1111 | 213.10     | 1010     | 1110 |     |     |

| 101  | 110  | 011  | 111        |          | 101  | 011 | 100 |

| 5    | 6    | 3    | 7          | D. R. P. | 5    | 3   | 4   |

=5637.534

#### **Complements:**

In digital computers to simplify the subtraction operation & for logical manipulation complements are used. There are two types of complements used in each radix system.

- i) The radix complement or r's complement

- ii) The diminished radix complement or (r-1)'s complement

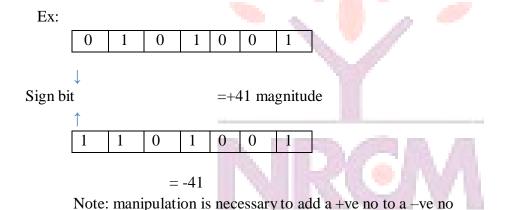

#### Representation of signed no.s binary arithmetic in computers:

- Two ways of rep signed no.s

- 1. Sign Magnitude form

- 2. Complemented form

- Two complimented forms

- 1. 1's compliment form

- 2. 2's compliment form

Advantage of performing subtraction by the compliment method is reduction in the hardware. (instead of addition & subtraction only adding ckt's are needed.)

i.e, subtraction is also performed by adders only.

Instead of subtracting one no. from other the compliment of the subtrahend is added to minuend. In sign magnitude form, an additional bit called the sign bit is placed in front of the no. If the sign bit is 0, the no. is +ve, If it is a 1, the no is \_ve.

Representation of signed no.s using 2's or 1's complement method:

If the no. is +ve, the magnitude is rep in its true binary form & a sign bit 0 is placed in front of the MSB.I f the no is \_ve , the magnitude is rep in its 2's or 1's compliment form &a sign bit 1 is placed in front of the MSB.

### ENGINEEDING CO

| Given no. | Sign mag form | 2's comp form | 1's comp form |

|-----------|---------------|---------------|---------------|

| 01101     | +13           | +13           | +13           |

| 010111    | +23           | +23           | +23           |

| 10111     | -7            | -7            | -8            |

| 1101010   | -42           | -22           | -21           |

#### **Special case in 2's comp representation:**

Whenever a signed no. has a 1 in the sign bit & all 0's for the magnitude bits, the decimal equivalent is  $-2^n$ , where n is the no of bits in the magnitude.

Ex: 1000= -8 & 10000=-16

#### **Characteristics of 2's compliment no.s:**

#### Properties:

- 1. There is one unique zero

- 2. 2's comp of 0 is 0

- 3. The leftmost bit can't be used to express a quantity. it is a 0 no. is +ve.

- 4. For an n-bit word which includes the sign bit there are  $(2^{n-1}-1)$  +ve integers,  $2^{n-1}$  -ve integers & one 0, for a total of  $2^n$  uniquestates.

- 5. Significant information is contained in the 1's of the +ve no.s & 0's of the \_ve no.s

- 6. A \_ve no. may be converted into a +ve no. by finding its 2's comp.

### **Signed binary numbers:**

| Decimal | Sign 2's comp form | Sign 1's comp form | Sign mag form |

|---------|--------------------|--------------------|---------------|

| +7      | 0111               | 0111               | 0111          |

| +6      | 0110               | 0110               | 0110          |

| +5      | 0101               | 0101               | 0101          |

| +4      | 0100               | 0100               | 0100          |

| +3      | 0011               | 0011               | 0011          |

| +2      | 0010               | 0010               | 0010          |

| +1      | 0011               | 0011               | 0011          |

| +0      | 0000               | 0000               | 0000          |

| -0 | TOCIANI | 1111 | 1000 |

|----|---------|------|------|

| -1 | 1111    | 1110 | 1001 |

| -2 | 1110    | 1101 | 1010 |

| -3 | 1101    | 1100 | 1011 |

| -4 | 1100    | 1011 | 1100 |

| -5 | 1011    | 1010 | 1101 |

| -6 | 1010    | 1001 | 1110 |

| -7 | 1001    | 1000 | 1111 |

| 8  | 1000    |      |      |

#### Methods of obtaining 2's comp of a no:

- In 3 ways

- 1. By obtaining the 1's comp of the given no. (by changing all 0's to 1's & 1's to 0's) & then adding 1.

- 2. By subtracting the given n bit no N from 2<sup>n</sup>

- 3. Starting at the LSB, copying down each bit upto & including the first 1 bit encountered, and complimenting the remaining bits.

Ex: Express -45 in 8 bit 2's comp form

+45 in 8 bit form is 00101101

#### I method:

1's comp of 00101101 & the add 1 00101101 11010010

+1

11010011

is 2's comp form

#### II method:

Subtract the given no. N from 2<sup>n</sup>

$2^n = 100000000$

Subtract 45=-00101101

. . . .

\_11010011

is 2's comp

III method:

Original no: 00101101

Copy up to First 1 bit 1 Compliment remaining : 1101001

bits 11010011

Ex:

I method

01001001.1100 10110110.0011

+1

10110110.0100 is 2's

II method:

$2^8 = 100000000.0000$

Sub 73.75=-01001001.1100

10110110.0100 is 2's comp

III method:

Orginalno : 01001001.1100

Copy up to 1'st bit 100

Comp the remaining bits: 10110110.0

10110110.0100

#### 2's compliment Arithmetic:

• The 2's comp system is used to rep –ve no.s using modulus arithmetic. The word length of a computer is fixed, i.e, if a 4 bit no. is added to another 4 bit no. the result will be only of 4 bits. Carry if any, from the fourth bit will overflow called the Modulus arithmetic.

Ex:1100+1111=1011

• In the 2's compl subtraction, add the 2's comp of the subtrahend to the minuend. If there is a carry out, ignore it, look at the sign bit I,e, MSB of the sum term. If the MSB is a 0, the result is positive. & it is in true binary form. If the MSB is a `( carry in or no carry at all) the result is negative. & is in its 2's comp form. Take its 2's comp to find its magnitude in binary.

Ex:Subtract 14 from 46 using 8 bit 2's comp arithmetic:

+14 = 00001110

-14 = 11110010 2's comp

+46 = 00101110

-14 = +11110010 2's comp form of -14

-32 (1)00100000 ignore carry

form. So the result is +00100000=+32.

EX: Add -75 to +26 using 8 bit 2's comp arithmetic

+75 = 01001011

-75 = 10110101 2's comp

+26 = 00011010

-75 = +10110101 2's comp form of -75

vour robis to success...

# NARSIMHA REDDY ENGINEERING COLLEGE

-49 11001111

No carry

No carry, MSB is a 1, result is \_ve & is in 2's comp. The magnitude is 2's comp of 11001111. i.e, 00110001 = 49. so result is -49

Ex: add -45.75 to +87.5 using 12 bit arithmetic

+87.5 = 01010111.1000

-45.75 = +11010010.0100

-41.75 (1)00101001.1100 ignore carry

MSB is 0, result is +ve. = +41.75

#### 1's compliment of n number:

- It is obtained by simply complimenting each bit of the no,. & also, 1's comp of a no, is subtracting each bit of the no. form 1. This complemented value rep the – ve of the original no. One of the difficulties of using 1's comp is its rep of zero. Both 00000000 & its 1's comp 111111111 rep zero.

- The 00000000 called +ve zero& 11111111 called -ve zero.

Ex: -99 & -77.25 in 8 bit 1's comp

+99

01100011

-99

10011100

+77.25 =

01001101.0100

-77.25 =

10110010.1011

#### 1's compliment arithmetic:

In 1's comp subtraction, add the 1's comp of the subtrahend to the minuend. If there is a carryout, bring the carry around & add it to the LSB called the end around carry. Look at the sign bit (MSB). If this is a 0, the result is +ve & is in true binary. If the MSB is a 1 (carry or no carry), the result is -ve & is in its is comp form. Take its 1's comp to get the magnitude inn binary.

Ex: Subtract 14 from 25 using 8 bit 1's EX: ADD -25 to +14

> 25 00011001 -45

+14= 00001110

11110001

-25 =+11100110

+11

(1)00001010 -11 11110100

#### 00001011 MSB is a 0 so result is +ve (binary)

result=-ve=-11<sub>10</sub>

$=+11_{10}$

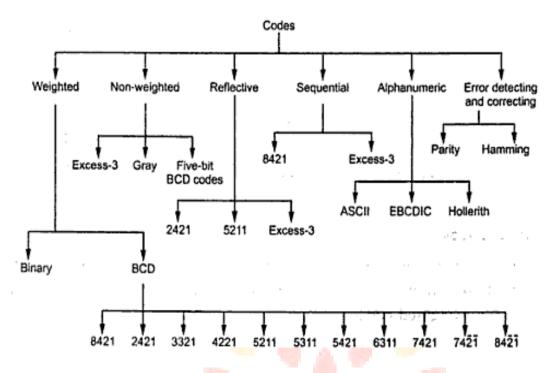

#### **Binary codes**

Binary codes are codes which are represented in binary system with modification from the original ones.

☐ Weighted Binary codes

□ Non Weighted Codes

Weighted binary codes are those which obey the positional weighting principles, each position of the number represents a specific weight. The binary counting sequence is an example.

| Decimal | BCD<br>8421 | Excess-3 | 84-2-1 | 2421 | 5211 | Bi-Quinary<br>5043210 |   | 5 | 0 | 4 | 3 | 2 | 1 | 0 |

|---------|-------------|----------|--------|------|------|-----------------------|---|---|---|---|---|---|---|---|

| 0       | 0000        | 0011     | 0000   | 0000 | 0000 | 0100001               | 0 |   | Χ |   |   |   |   | Χ |

| 1       | 0001        | 0100     | 0111   | 0001 | 0001 | 0100010               | 1 |   | Χ |   |   |   | Χ |   |

| 2       | 0010        | 0101     | 0110   | 0010 | 0011 | 0100100               | 2 |   | X |   |   | Χ |   |   |

| 3       | 0011        | 0110     | 0101   | 0011 | 0101 | 0101000               | 3 |   | Χ |   | Χ |   |   |   |

| 4       | 0100        | 0111     | 0100   | 0100 | 0111 | 0110000               | 4 |   | X | Χ |   |   |   |   |

| 5       | 0101        | 1000     | 1011   | 1011 | 1000 | 1000001               | 5 | Χ |   |   |   |   |   | Χ |

| 6       | 0110        | 1001     | 1010   | 1100 | 1010 | 1000010               | 6 | X |   |   |   |   | X |   |

| 7       | 0111        | 1010     | 1001   | 1101 | 1100 | 1000100               | 7 | Χ |   |   |   | Х |   |   |

| 8       | 1000        | 1011     | 1000   | 1110 | 1110 | 1001000               | 8 | X |   |   | X |   |   |   |

| 9       | 1001        | 1111     | 1111   | 1111 | 1111 | 1010000               | 9 | Χ |   | Χ |   |   |   |   |

#### **Reflective Code**

A code is said to be reflective when code for 9 is complement for the code for 0, and

so is for 8 and 1 codes, 7 and 2, 6 and 3, 5 and 4. Codes 2421, 5211, and excess-3 are reflective, whereas the 8421 code is not.

#### **Sequential Codes**

A code is said to be sequential when two subsequent codes, seen as numbers in binary representation, differ by one. This greatly aids mathematical manipulation of data. The 8421 and Excess-3 codes are sequential, whereas the 2421 and 5211 codes are not.

#### Non weighted codes

Non weighted codes are codes that are not positionally weighted. That is, each position within the binary number is not assigned a fixed value. Ex: Excess-3 code

#### Excess-3 Code

Excess-3 is a non weighted code used to express decimal numbers. The code derives its name from the fact that each binary code is the corresponding 8421 code plus 0011(3).

#### **Gray Code**

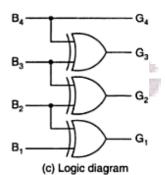

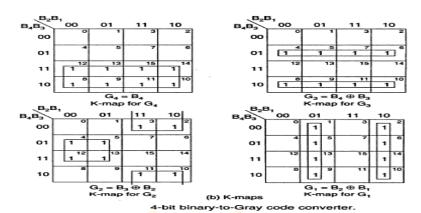

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next. The Gray code is non-weighted code, as the position of bit does not contain any weight. The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a unit-distance code. In digital Gray code has got a special place.

| Decimal<br>Number | Binary<br>Code | Gray Code | Decimal<br>Number | Binary<br>Code | Gray Code |

|-------------------|----------------|-----------|-------------------|----------------|-----------|

| 0                 | 0000           | 0000      | 8                 | 1000           | 1100      |

| 1                 | 0001           | 0001      | 9                 | 1001           | 1101      |

| 2                 | 0010           | 0011      | 10                | 1010           | 1111      |

| 3                 | 0011           | 0010      | 11                | 1011           | 1110      |

| 4                 | 0100           | 0110      | 12                | 1100           | 1010      |

| 5                 | 0101           | 0111      | 13                | 1101           | 1011      |

| 6                 | 0110           | 0101      | 14                | 1110           | 1001      |

| 7                 | 0111           | 0100      | 15                | 1111           | 1000      |

#### **Binary to Gray Conversion**

|  | Gray | Code | MSB | is | binary | code | MSB. |

|--|------|------|-----|----|--------|------|------|

|--|------|------|-----|----|--------|------|------|

- ☐ Gray Code MSB-1 is the XOR of binary code MSB and MSB-1.

- ☐ MSB-2 bit of gray code is XOR of MSB-1 and MSB-2 bit of binary code.

- ☐ MSB-N bit of gray code is XOR of MSB-N-1 and MSB-N bit of binary code.

#### 8421 BCD code (Natural BCD code):

Each decimal digit 0 through 9 is coded by a 4 bit binary no. called natural binary codes. Because of the 8,4,2,1 weights attached to it. It is a weighted code & also sequential. it is useful for mathematical operations. The advantage of this code is its case of conversion to & from decimal. It is less efficient than the pure binary, it require more bits.

Ex:  $14 \rightarrow 1110$  in binary

But as 0001 0100 in 8421 ode.

The disadvantage of the BCD code is that , arithmetic operations are more complex than they are in pure binary . There are 6 illegal combinations 1010,1011,1100,1101,1110,1111 in these codes, they are not part of the 8421 BCD code system . The disadvantage of 8421 code is, the rules of binary addition 8421 no, but only to the individual 4 bit groups.

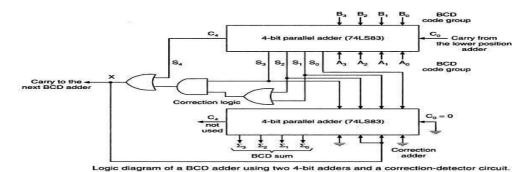

#### **BCD Addition:**

It is individually adding the corresponding digits of the decimal no,s expressed in 4 bit binary groups starting from the LSD . If there is no carry & the sum term is not an illegal code , no correction is needed .If there is a carry out of one group to the next group or if the sum term is an illegal code then  $6_{10}(0100)$  is added to the sum term of that group & the resulting carry is added to the next group.

SIMHA RE

IG COLLEGE

Ex: Perform decimal additions in 8421 code

$$(a)25+13$$

In BCD 25= 0010 0101 In BCD +13 =+0001 0011

38 0011 1000

No carry, no illegal code .This is the corrected sum

(b). 679.6 + 536.8679.6 0110 0111 1001 .0110 in BCD = +536.8 = +01010011 0010 .1000 in BCD 1216.4 1011 1010 0110 . 1110 illegal codes add 0110 to each +0110+ 0011+0110. + 0110(1)0101. (1)0100 (1)0001(1)0000propagate carry +1+1+1+10001 0010 0001 0110 0100 1 2

#### **BCD Subtraction:**

Performed by subtracting the digits of each 4 bit group of the subtrahend the digits from the corresponding 4- bit group of the minuend in binary starting from the LSD . if there is no borrow from the next group, then  $6_{10}(0110)$  is subtracted from the difference term of this group.

(a)38-15

23 0010 0011

No borrow, so correct difference.

.(b) 206.7-147.8

#### BCD Subtraction using 9's & 10's compliment methods:

Form the 9's & 10's compliment of the decimal subtrahend & encode that no. in the 8421 code . the resulting BCD no.s are then added.

= 136.7

St. L. L. 17, 11

#### Excess three(xs-3)code:

It is a non-weighted BCD code .Each binary codeword is the corresponding 8421 codeword plus 0011(3).It is a sequential code & therefore, can be used for arithmetic operations..It is a self-complementing code.s o the subtraction by the method of compliment addition is more direct in xs-3 code than that in 8421 code. The xs-3 code has six invalid states 0000,0010,1101,1110,1111. It has interesting properties when used in addition & subtraction.

#### **Excess-3 Addition:**

Add the xs-3 no.s by adding the 4 bit groups in each column starting from the LSD. If there is no carry starting from the addition of any of the 4-bit groups, subtract 0011 from the sum term of those groups (because when 2 decimal digits are added in xs-3 & there is no carry, result in xs-6). If there is a carry out, add 0011 to the sum term of those groups (because when there is a carry, the invalid states are skipped and the result is normal binary).

#### **Excess -3 (XS-3) Subtraction:**

Subtract the xs-3 no.s by subtracting each 4 bit group of the subtrahend from the corresponding 4 bit group of the minuend starting form the LSD .if there is no borrow from the next 4-bit group add 0011 to the difference term of such groups (because when decimal digits are subtracted in xs-3 & there is no borrow , result is normal binary). If there is a borrow , subtract 0011 from the differenceterm(b coz taking a borrow is equivalent to adding six invalid states , result is in xs-6)

Ex: 267-175

267 = 0101 1001 1010 -175= -0100 1010 1000

0011 1100 +0011 =92<sub>10</sub>

#### Xs-3 subtraction using 9's & 10's compliment methods:

Subtraction is performed by the 9's compliment or 10's compliment Ex:687-348 The subtrahend (348) xs -3 code & its compliment are:

9's comp of 348 = 651 Xs-3 code of 348 = 0110 0111 1011 1's comp of 348 in xs-3 = 1001 1000 0100 Xs=3 code of 348 in xs=3 = 1001 1000 0100

339 (1)338 +1 end around carry

339 corrected difference in decimal

1001 1011 1010 687 in xs-3

+1001 1000 0100 1's comp 348 in xs-3

NRGM

vour robis lo sudcess...

NARSIMHA REDDY ENGINEERING COLLEGE

(1)0010(1)00111110 carry generated +1+1propagate carry 0010 1110 (1)0011+1end around carry 0011 0011 1111 (correct 1111 by sub0011 and +0011+0011+0011correct both groups of 0011 by adding 0011) 1100 0110 corrected diff in  $xs-3 = 330_{10}$ 0110

#### The Gray code (reflective -code):

Gray code is a non-weighted code & is not suitable for arithmetic operations. It is not a BCD code . It is a cyclic code because successive code words in this code differ in one bit position only i.e, it is a unit distance code. Popular of the unit distance code. It is also a reflective code i.e, both reflective & unit distance. The n least significant bits for  $2^n$  through  $2^{n+1}-1$  are the mirror images of thosr for 0 through  $2^n-1$ . An N bit gray code can be obtained by reflecting an N-1 bit code about an axis at the end of the code, & putting the MSB of 0 above the axis & the MSB of 1 below the axis.

#### Reflection of gray codes:

| 6 |       | DC    | A L   | ALL   | A D     | EDD          |

|---|-------|-------|-------|-------|---------|--------------|

|   | 4     | Gray  | Code  | 1 IV  |         |              |

| ú | 1 bit | 2 bit | 3 bit | 4 bit | Decimal | 4 bit binary |

| ı | 0     | 00    | 000   | 0000  | 0       | 0000         |

|   | 1     | 01    | 001   | 0001  | 1       | 0001         |

|   |       | 11    | 011   | 0011  | 2       | 0010         |

|   |       | 10    | 010   | 0010  | 3       | 0011         |

|   |       |       | 110   | 0110  | 4       | 0100         |

|   |       |       | 111   | 0111  | 5       | 0101         |

|   |       |       | 101   | 0101  | 6       | 0110         |

|   |       |       | 110   | 0100  | 7       | 0111         |

|  | 1100 | 8  | 1000 |

|--|------|----|------|

|  | 1101 | 9  | 1001 |

|  | 1111 | 10 | 1010 |

|  | 1110 | 11 | 1011 |

|  | 1010 | 12 | 1100 |

|  | 1011 | 13 | 1101 |

|  | 1001 | 14 | 1110 |

|  | 1000 | 15 | 1111 |

#### **Binary to Gray conversion:**

N bit binary no is rep by  $B_n B_{n-1} = B_1$ Gray code equivalent is by  $G_n G_{n-1} - G_1$

B<sub>n</sub>, G<sub>n</sub> are the MSB's then the gray code bits are obtaind from the binary code as

Procedure: ex-or the bits of the binary no with those of the binary no shifted one position to the right. The LSB of the shifted no. is discarded & the MSB of the gray code no.is the same as the MSB of the original binaryno.

**A A A** EX: 10001

(a). Binary:

Gray:

Binary:  $1 \quad 0 \quad 0 \quad 1$ Shifted binary:  $1 \quad 0 \quad 0 \quad (1)$ (b).

ENGINEER ON 1 - gray C

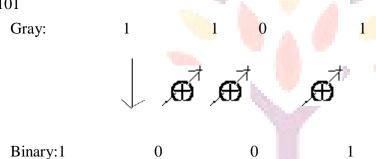

#### **Gray to Binary Conversion:**

If an n bit gray no. is rep by  $G_n G_{n-1}$ ..... $G_1$

its binary equivalent by B<sub>n</sub> B<sub>n-1</sub> ......B<sub>1</sub> then the binary bits are obtained from gray bits as

|             | $\sim$                  | $\sim$              | $\sim$         |

|-------------|-------------------------|---------------------|----------------|

| $B_n = G_n$ | $B_{n-1}=B_n$ $G_{n-1}$ | $B_{n-2} = G_{n-2}$ | <br>$B1 = B_2$ |

|             |                         |                     | C              |

|             |                         |                     | $G_1$          |

To convert no. in any system into given no. first convert it into binary & then binary to gray. To convert gray no into binary no & convert binary no into require no system.

Ex: 10110010(gray) =  $110111100_2$ = DC<sub>16</sub>= $334_8$ = $220_{10}$

EX:1101

Ex:  $3A7_{16} = 0011,1010,0111_2 = 1001110100(gray)$

527<sub>8</sub>=101,011,011<sub>2</sub>=111110110(gray) 652<sub>10</sub>=1010001100<sub>2</sub>=1111001010(gray)

#### XS-3 gray code:

In a normal gray code, the bit patterns for 0(0000) & 9(1101) do not have a unit distance between them i.e, they differ in more than one position. In xs-3 gray code, each decimal digit is encoded with gray code patter of the decimal digit that is greater by 3. It has a unit distance between the patterns for 0 & 9.

XS-3 gray code for decimal digits 0 through 9

| Decimal digit | Xs-3 gray code | Decimal digit | Xs-3 gray code |

|---------------|----------------|---------------|----------------|

| 0             | 0010           | 5             | 1100           |

| 1             | 0110           | 6             | 1101           |

| 2             | 0111           | 7             | 1111           |

| 3             | 0101           | 8             | 1110           |

| 4             | 0100           | 9             | 1010           |

Binary codes block diagram

Error – Detecting codes: When binary data is transmitted & processed, it is susceptible to noise that can alter or distort its contents. The 1's may get changed to 0's & 1's .because digital systems must be accurate to the digit, error can pose a problem. Several schemes have been devised to detect the occurrence of a single bit error in a binary word, so that whenever such an error occurs the concerned binary word can be corrected & retransmitted.

**Parity:** The simplest techniques for detecting errors is that of adding an extra bit known as parity bit to each word being transmitted. Two types of parity: Oddparity, evenparity forodd parity, the parity bit is set to a \_0' or a \_1' at the transmitter such that the total no. of 1 bit in the word including the parity bit is an odd no. For even parity, the parity bit is set to a \_0' or a \_1' at the transmitter such that the parity bit is an even no.

| Decimal | 8421 code | Odd parity | Even parity |

|---------|-----------|------------|-------------|

| 0       | 0000      | 11/4 N     | 0           |

| 1       | 0001      | 0          | 1           |

| 2       | 0010      | 0          | 1           |

| 3       | 0011      | 1 1 1      | 0           |

| 4       | 0100      | 0          | 1           |

| 5       | 0100      | 1          | 0           |

| 6       | 0110      | 1          | 0           |

| 7       | 0111      | 0          | 1           |

| 8       | 1000      | 0          | 1           |

| 9       | 1001      | 1          | 0           |

When the digit data is received . a parity checking circuit generates an error signal if the total no of 1's is even in an odd parity system or odd in an even parity system. This parity check can always detect a single bit error but cannot detect 2 or more errors with in the same word. Odd parity is used more often than even parity does not detect the situation. Where all 0's are created by a short ckt or some other fault condition.

Ex: Even parity scheme

(a) 10101010 (b) 11110110 (c)10111001

Ans:

- (a) No. of 1's in the word is even is 4 so there is no error

- (b) No. of 1's in the word is even is 6 so there is no error

- (c) No. of 1's in the word is odd is 5 so there is error

Ex: odd parity

(a) 10110111 (b) 10011010 (c) 11101010

Ans:

- (a) No. of 1's in the word is even is 6 so word has error

- (b) No. of 1's in the word is even is 4 so word has error

- (c) No. of 1's in the word is odd is 5 so there is no error

#### **Checksums:**

Simple parity can't detect two errors within the same word. To overcome this, use a sort of 2 dimensional parity. As each word is transmitted, it is added to the sum of the previously transmitted words, and the sum retained at the transmitter end. At the end of transmission, the sum called the check sum. Up to that time sent to the receiver. The receiver can check its sum with the transmitted sum. If the two sums are the same, then no errors were detected at the receiver end. If there is an error, the receiving location can ask for retransmission of the entire data, used in teleprocessing systems.

#### **Block parity:**

Block of data shown is create the row & column parity bits for the data using odd parity. The parity bit 0 or 1 is added column wise & row wise such that the total no. of 1's in each column & row including the data bits & parity bit is odd as

| Data  | Parity bit |

|-------|------------|

| 10110 | 0          |

| 10001 | 1          |

| 10101 | 0          |

| 00010 | 0          |

| 11000 | 1          |

| 00000 | 1          |

| 11010 | 0          |

| data  |

|-------|

| 10110 |

| 10001 |

| 10101 |

| 00010 |

| 11000 |

| 00000 |

| 11010 |

#### **Error** – **Correcting Codes:**

A code is said to be an error –correcting code, if the code word can always be deduced from an erroneous word. For a code to be a single bit error correcting code, the minimum distance of that code must be three. The minimum distance of that code is the smallest no. of bits by which any two code words must differ. A code with minimum distance of 3 can't only correct single bit errors but also detect ( can't correct) two bit errors, The key to error correction is that it must be possible to detect & locate erroneous that it must be possible to detect & locate erroneous digits. If the location of an error has been determined. Then by complementing the erroneous digit, the message can be corrected, error correcting, code is the Hamming code, In this, to each group of m information or message or data bits, K parity checking bits denoted by P1,P2,-------pk located at positions  $2^{k-1}$  from left are added to form an (m+k) bit code word. To correct the error, k parity checks are performed on selected digits of each code word, & the position of the error bit is located by forming an error word, & the error bit is then complemented. The k bit error word is generated by putting a 0 or a 1 in the  $2^{k-1}$ th position depending upon whether the check for parity involving the parity bit  $P_k$  is satisfied or not. Error positions & their corresponding values:

# NARSIMHA REDDY ENGINEERING COLLEGE

| Error Position | For 15 bit code   | For 12 bit code   | For 7 bit code |

|----------------|-------------------|-------------------|----------------|

|                | $C_4 C_3 C_2 C_1$ | $C_4 C_3 C_2 C_1$ | $C_3 C_2 C_1$  |

| 0              | 0000              | 0000              | 0 0 0          |

| 1              | 0 0 0 1           | 0 0 0 1           | 0 0 1          |

| 2              | 0010              | 0 0 1 0           | 0 1 0          |

| 3              | 0 0 1 1           | 0 0 1 1           | 0 1 1          |

| 4              | 0100              | 0100              | 100            |

| 5              | 0 1 0 1           | 0 1 0 1           | 101            |

| 6              | 0 1 10            | 0 1 10            | 1 1 0          |

| 7              | 0 1 1 1           | 0 1 1 1           | 1 1 1          |

| 8              | 1 0 0 0           | 1 0 0 0           |                |

| 9              | 1 0 0 1           | 1 0 0 1           |                |

| 10             | 1 0 1 0           | 1 0 1 0           |                |

| 11             | 1 0 1 1           | 1 0 1 1           |                |

| 12             | 1 1 0 0           | 1 1 0 0           |                |

| 13             | 1 1 0 1           | A -               |                |

| 14             | 1 1 1 0           | W 10 -            |                |

| 15             | 1 1 1 1           | * //              |                |

### 7- bit Hamming code:

To transmit four data bits, 3 parity bits located at positions 2<sup>0</sup> 21&2<sup>2</sup> from left are added to make a 7 bit codeword which is then transmitted.

The word format

vour robis lo success...

# NARSIMHA REDDY ENGINEERING COLLEGE

| $\mathbf{P}_1$ | $P_2$ | $D_3$ | $P_4$ | $D_5$ | $D_6$ | $D_7$ |

|----------------|-------|-------|-------|-------|-------|-------|

D—Data bits P-

| Decimal Digit | For BCD        | For Excess-3   |

|---------------|----------------|----------------|

|               | P1P2D3P4D5D6D7 | P1P2D3P4D5D6D7 |

| 0             | 0 0 0 0 0 0 0  | 1 0 0 0 0 1 1  |

| 1             | 1 1 0 1 0 0 1  | 1 0 0 1 1 0 0  |

| 2             | 0 1 0 1 0 1 1  | 0 1 0 0 1 0 1  |

| 3             | 1 0 0 0 0 1 1  | 1 1 0 0 1 1 0  |

| 4             | 1 0 0 1 1 0 0  | 0 0 0 1 1 1 1  |

| 5             | 0 1 0 0 1 0 1  | 1 1 1 0 0 0 0  |

| 6             | 1 1 0 0 1 1 0  | 0 0 1 1 0 0 1  |

| 7             | 0 0 0 1 1 1 1  | 1 0 1 1 0 1 0  |

| 8             | 1 1 1 0 0 0 0  | 0 1 1 0 0 1 1  |

| 9             | 0 0 1 1 0 0 1  | 0 1 1 1 1 0 0  |

vour robis lo success...

# NARSIMHA REDDY ENGINEERING COLLEGE

Ex: Encode the data bits 1101 into the 7 bit even parity Hamming Code

The bit pattern is

P1P2D3P4D5D6D7

1 1 0 1

Bits 1,3,5,7 ( $P_1$  111) must have even parity, so  $P_1$ =1

Bits 2, 3, 6,  $7(P_2 101)$  must have even parity, so  $P_2=0$

Bits 4,5,6,7 (P<sub>4</sub> 101) must have even parity, so  $P_4 = 0$

The final code is 1010101

EX: Code word is 1001001

Bits 1,3,5,7 ( $C_1$  1001)  $\rightarrow$ no error  $\rightarrow$ put a 0 in the 1's position $\rightarrow$  $C_1=0$

Bits 2, 3, 6,  $7(C_2 0001)$ )  $\rightarrow$  error  $\rightarrow$ put a 1 in the 2's position $\rightarrow$ C2=1

Bits 4,5,6,7 (C<sub>4</sub> 1001))  $\rightarrow$ no error  $\rightarrow$ put a 0 in the 4's position $\rightarrow$ C3=0

**15-bit Hamming Code:** It transmit 11 data bits, 4 parity bits located 2<sup>0</sup> 2<sup>1</sup> 2<sup>2</sup> 2<sup>3</sup>

Word format is

| $\mathbf{P}_1$ | $P_2$ | $D_3$ | P <sub>4</sub> | $D_5$ | $D_6$ | $D_7$ | P <sub>8</sub> | D <sub>9</sub> | D10 | D11 | D12 | D13 | D14 | D15 |

|----------------|-------|-------|----------------|-------|-------|-------|----------------|----------------|-----|-----|-----|-----|-----|-----|

|----------------|-------|-------|----------------|-------|-------|-------|----------------|----------------|-----|-----|-----|-----|-----|-----|

**12-Bit Hamming Code:** It transmit 8 data bits, 4 parity bits located at position  $2^0 \ 2^1 \ 2^2 \ 2^3$

Word format is

| $\mathbf{P}_1$ | $P_2$ | $D_3$ | $P_4$ | $D_5$ | $D_6$ | $\mathbf{D}_7$ | $P_8$ | $D_9$ | D10 | D11 | D12 |

|----------------|-------|-------|-------|-------|-------|----------------|-------|-------|-----|-----|-----|

#### **Alphanumeric Codes:**

These codes are used to encode the characteristics of alphabet in addition to the decimal digits. It is used for transmitting data between computers & its I/O device such as printers, keyboards & video display terminals.Popular modern alphanumeric codes are ASCII code & EBCDIC code.

#### **Boolean algebra**

In 1854, George Boole developed an algebraic system now called Boolean algebra. In 1938, Claude E. Shannon introduced a two-valued Boolean algebra called switching algebra that represented the properties of bistable electrical switching circuits. For the formal definition of Boolean algebra, we shall employ the postulates formulated by E. V. Huntington in 1904.

Boolean algebra is a system of mathematical logic. It is an algebraic system consisting of the set of elements (0, 1), two binary operators called OR, AND, and one unary operator NOT. It is the basic mathematical tool in the analysis and synthesis of switching circuits. It is a way to express logic functions algebraically.

#### Axioms and laws of Boolean algebra

Axioms or Postulates of Boolean algebra are a set of logical expressions that we accept without

was af and ...as a ...bisb ...s son b..ild a sat af ...asf..l the answer

AND Operation OR Operation NOT Operation

Axiom1: 0.0=0 0+0=0  $-\theta$ 1 Axiom2: 0.1=0 0+1=1  $-\frac{1}{2}$ 0

Axiom3: 1.0=0 1+0=1 Axiom4: 1.1=1 1+1=1

#### **Complementation law**

Law1:  $\theta$ 1 Law3: if A=0,then  $\overline{A}$ 1 Law2:  $\overline{\pm}$ 0 Law4: if A=1,then  $\overline{A}$ =0

Law5: if AA (double inversion law)

#### **AND Law**

Law1: A.0=0 (Null law) Law2: A.1=A (Identity law) Law3: A.A=A (Impotence law)

Law4: A. A0

#### **OR Law**

Law1: A+0=A Law2: A+1=1

Law3: A+A=A (Impotence law)

Law4: A+ A1

vour robis lo success...

NARSIMHA REDDY ENGINEERING COLLEGE

#### **Basic Theorems and Properties of Boolean algebra**

#### **Commutative law**

Law1: A+B=B+A Law2: A.B=B.A

**Associative law**

Law1: A + (B + C) = (A + B) + C Law2: A(B.C) = (A.B)C

**Distributive law**

Law1: A.(B + C) = AB + AC Law2: A + BC = (A + B).(A + C)

**Absorption law**

Law1: A + AB = A Law2: A(A + B) = A

Solution: A(1+B) Solution: A.A+A.B A+A.B

A(1+B)

**DeMorgan Theorems**

Theorem 1:  $\overline{AB} = \overline{AB}$  Theorem 2:  $\overline{AB} = \overline{AB}$

**Redundant Literal Rule**

Rule1: A+AB=A+B

Solution:  $A + \overline{AB}$  Solution:  $A.(\overline{AB})$

$(A+\overline{A}).(A+B)$   $\therefore$  A+BC=(A+B).(A+C) A.AA.B A+B  $\therefore A+\overline{A}=1$  AB

**Consensus Theorem**

Theorem 1. AB + A'C + BC = AB + A'C Theorem 2. (A+B). (A'+C). (B+C) = (A+B). (A'+C)

The BC term is called the consensus term and is redundant. The consensus term is formed from a PAIR OF TERMS in which a variable (A) and its complement (A') are present; the consensus term is formed by multiplying the two terms and leaving out the selected variable and its complement

#### Consensus Theorem1 Proof:

AB+A'C+BC=AB+A'C+(A+A')BC =AB+A'C+ABC+A'BC =AB(1+C)+A'C(1+B) =AB+A'C

#### **Principle of Duality**

Each postulate consists of two expressions statement one expression is transformed into the other by interchanging the operations (+) and  $(\cdot)$  as well as the identity elements 0 and 1. Such expressions are known as duals of each other.

If some equivalence is proved, then its dual is also immediately true.

E.g. If we prove: (x.x)+(x'+x')=1, then we have by duality:  $(x+x)\cdot(x'.x')=0$

The Huntington postulates were listed in pairs and designated by part (a) and part (b) in below table.

Table for Postulates and Theorems of Boolean algebra

| Part-A                                       | Part-B                             |  |  |

|----------------------------------------------|------------------------------------|--|--|

| A+0=A                                        | A.0=0                              |  |  |

| A+1=1                                        | A.1=A                              |  |  |

| A+A=A (Impotence law)                        | A.A=A (Impotence law)              |  |  |

| A+ A1                                        | A. A0                              |  |  |

| AA (double inversion law)                    |                                    |  |  |

| Commutative law: A+B=B+A                     | A.B=B.A                            |  |  |

| Associative law: $A + (B + C) = (A + B) + C$ | A(B.C) = (A.B)C                    |  |  |

| <b>Distributive law</b> : A.(B + C) = AB+ AC | A + BC = (A + B).(A + C)           |  |  |

| Absorption law: A +AB =A                     | A(A+B)=A                           |  |  |

| DeMorgan Theorem: (A) = AB                   | (AB)=A B                           |  |  |

| Redundant Literal Rule: A+ AB=A+B            | A.(AB)=AB                          |  |  |

| Consensus Theorem: AB+ A'C + BC = AB + A'C   | (A+B). (A'+C).(B+C) = (A+B).(A'+C) |  |  |

# NARSIMHA REDDY ENGINEERING COLLEGE

#### **History of Digital ICs and their Classifications**

**Integrated circuit:** A collection of one or more gates fabricated on a single silicon chip is called an Integrated Circuit(IC) or it can be defined as an Integrated Circuit(IC) is a silicon wafer or a Die that contains two or more number of active such as diodes, transistors and some of passive components such as resistors, capacitors.

NOTE: The passive element Inductor can't be fabricated using ICs, Because they have magnetic flux

#### **History of IC:**

- There are many ways are available to design electronic logic circuit. First electrically controlled logic circuits were developed in 1930s at Bell laboratories based on relays.

- The first electronic digital computer named as ENIAC was developed in mid 1940s based on vacuum tubes. It has 100 feet long, 10 feet height, 3 feet deep and consumed 140kw of power.

- > By the invention of semiconductor diode and transistor after 1947 smaller, faster and more capable computers were designed.

- Eletter computers are designed by the invention of ICs which allowed multiples diodes, transistors and other components to be fabricated on a single chip of silicon in 1960s.

- The first IC family was introduced in 1960.

Classification of Digital ICs: Based on the size or number of logic components/gates fabricated per chip the ICs are classified into different Integrations as

- > Small Scale Integration (SSI): It have less than 100 components (about 10 gates).

- Medium Scale Integration (MSI): It contains between 100-1000 components or have more than 10 but less than 100 gates.

- Large Scale Integration (LSI): Here number of components is between 1000 and 10000 or have gates between 100-1000.

- ➤ Very Large Scale Integration (VLSI): It contains components between 10000-100000 per chip or gates between 1000-10000 per chip.

- ➤ Ultra Large Scale Integration (ULSI): It contains more than 100000 components per chip.

- ➤ Giant Scale Integration (GSI): It contains much more than 2000000 components per chip.

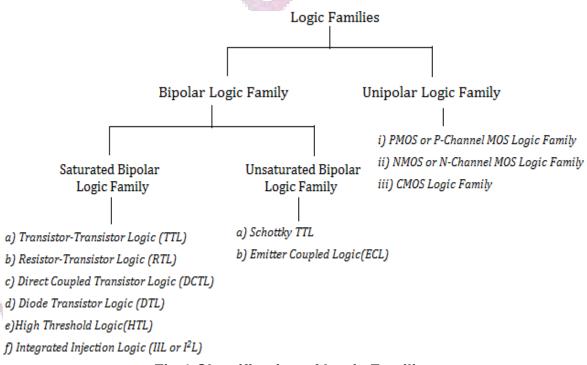

### Logic Families and their classifications: Logic Families:

It is a collection of different IC chips that have similar input, output and internal circuit characteristics i.e. group of compatible ICs with same logic levels and supply voltages but perform different logic functions. NOTE: 1) Chips from same family can be interconnected.

2) Chips from different family may not be compatible, means they may use different power supply voltages and input, output conditions.

### **Classification of Logic Families:**

Logic families are mainly classified as two types as

Bipolar Logic Families: It mainly uses bipolar devices like diodes, transistors in addition to passive elements like resistors and capacitors. These are sub classified as saturated bipolar logic family and unsaturated bipolar logic family. i) *Saturated Bipolar Logic Family:* In this family the transistors used in ICs are driven into saturation.

Examples: a) Transistor-Transistor Logic (TTL)

- b) Resistor-Transistor Logic (RTL)

- c) Direct Coupled Transistor Logic (DCTL)

- d) Diode Transistor Logic (DTL)

- e)High Threshold Logic(HTL)

- f) Integrated Injection Logic (IIL or I2L)

- ii)Unsaturated bipolar logic family: In this family the transistors used in ICs are not driven into saturation.

Examples: a) Schottky TTL b) Emitter Coupled Logic(ECL)

B) Unipolar Logic Families: It mainly uses Unipolar devices like MOSFETs in addition to passive elements like resistors and capacitors. These logic families have the advantages of high speed and lower power consumption

than Bipolar families. These are classified as

- i) PMOS or P-Channel MOS Logic Family

- ii) NMOS or N-Channel MOS Logic Family

- iii) CMOS Logic Family

Fig.1 Classification of Logic Families

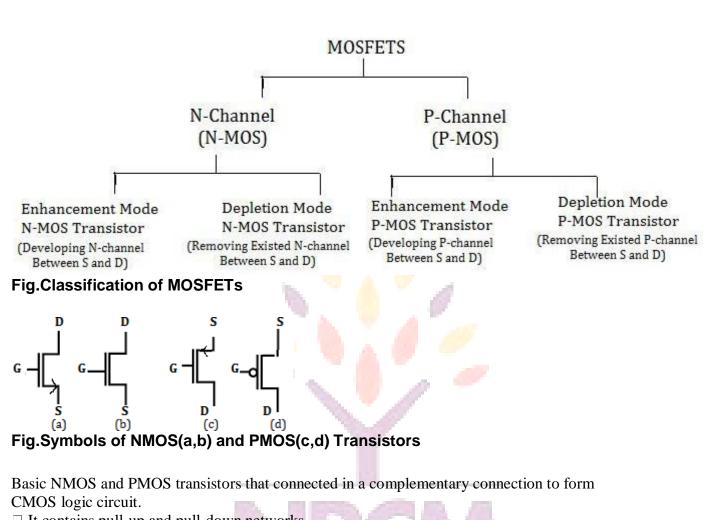

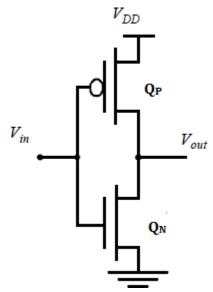

**CMOS Logic:** The basic building blocks in CMOS logic circuits are MOS transistors. All circuits that are implemented by CMOS logic have Basic CMOS circuit which will form by the Complementary connection of NMOS and PMOS transistors. So that this logic is named as Complementary Metal Oxide Semiconductor Logic. Metal Oxide Semiconductor transistor: ☐ A MOS transistor contains 4 terminals named as Gate(G), Source(S), Drain(D) and Substrate(Sb). ☐ Among 4 terminals Gate is an insulating terminal. So no conduction will takes place between remaining two(S and D) terminals. Hence it has highest resistance between Source and Drain. ☐ The voltage applied at the Gate terminal may create electric field that enhances or retards the flow of current between Source and Drain. Due to this field effect MOS transistors are called Field Effect Transistors (FET). ☐ Here the Resistance between Source and Drain also controlled by voltage applied at Gate terminal hence MOSFETs also called as *Voltage Controlled Resistors*. ☐ MOS transistors are classified into two types based on the use of the channel type as N-Channel or NMOS transistor and P-Channel or PMOS transistor. ☐ Both N-Channel or NMOS transistor and P-Channel or PMOS transistor are again sub divided into two types based on their mode of operation as Enhancement mode and Deletion mode transistors ☐ In Enhancement mode of operation a channel is developed between two terminals Source and Drain of respective MOS transistors.ie. If it is NMOS transistor then N- Channel and it is PMOS then PChannel transistor by applying required voltage at Gate terminal. ☐ In Depletion mode of operation the already existed channel will be removed between two terminals Source and Drain of respective MOS transistors.ie. If it is NMOS transistor then NChannel and it is PMOS then P-Channel transistor by applying required voltage at Gate terminal. ☐ In N-MOS Transistor if input voltage Vgs is Zero then resistance between Source and Drain Rds is very high in terms of M $\Omega$  and if  $V_{gs}$  is more positive voltage then  $R_{ds}$  is very low in terms of (0-10)  $\Omega$ . ☐ In P-MOS Transistor if input voltage V<sub>gs</sub> is Zero then resistance between Source and Drain R<sub>ds</sub> is very high in terms of M $\Omega$  and if  $V_{gs}$  is more negative voltage then  $R_{ds}$  is very low in terms of (0-10)  $\Omega$ . Note: A small current will flows through high resistance between Gate and Source or Drain junctions. □ Explain the Operation of basic CMOS circuit? **Basic CMOS**

NARSIMHA REDDY ENGINEERING COLLEGE

☐ It contains pull-up and pull-down networks. ☐ Pull-up network contains PMOS transistor and pull-down network consists of NMOS

Transistor. ☐ When input applied as logic '0'(L) the PMOS transistor is in ON condition and that translates

output to logic '1'(H), i.e., applied voltage is pulled up to 5V(H) from 0V(L) by PMOS transistor. Hence it is called as *Pull-Up transistor*.

☐ When input applied as logic '1'(H) the NMOS transistor is in ON condition and that translates output to logic '0'(L), i.e., applied voltage is pulled down to 0V(L) from 5V(H) by NMOS transistor. Hence it is called as Pull-Down transistor.

ENGINEERING COLLEGE

## Operation:

Case (i): When V<sub>in</sub>= 0 V, then NMOS transistor is OFF state, since its V<sub>GS</sub> = 0 V. PMOS is in ON state Since its V<sub>GS</sub> is large negative (-5V). So PMOS presents only a small resistance between V<sub>DD</sub> and output. Hence output is 5 V.

Case (ii): When  $V_{in}=5$  V, then PMOS transistor is in OFF state, since its  $V_{GS}=0$  V. NMOS is in ON state Since its  $V_{GS}$  is large positive (+5 V). So NMOS presents only a small resistance between output and ground. Hence output is 0 V.

Note: From case (i) & (ii) we can conclude that the operation of a basic CMOS circuit gives INVERTING operation.

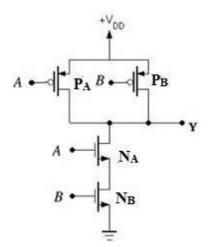

## 2 Input NAND gate using CMOS logic

NAND gate is one of the basic logic gates to perform the digital operation on the input signals.

- ☐ It is the combination of AND Gate followed by NOT gate i.e. it is the opposite operation of AND gate where the Logic NAND gate is complementary of AND gate.

- ☐ The logic output of NAND gate is low(FALSE) only when the inputs are high (TRUE).

- $\square$  To implementation 2 Input NAND gate using CMOS logic we require 2 pull-up PMOS and 2 pull-down NMOS transistors.

#### **Operation:**

**Case (i):** When A=B=0 V, then both NMOS transistors are in OFF state, since its V<sub>GSA</sub> = V<sub>GSB</sub> = 0 V. Both PMOS transistors (PA, PB) are in ON state. Since its V<sub>GSA</sub> and V<sub>GSB</sub> voltage is large negative (-5V). So PMOS transistors presents only a small resistance between V<sub>DD</sub> and output. Hence output is 5 V.

**Case (ii):** When A=B=5 V, then both PMOS transistors are in OFF state, since its input voltages V<sub>GSA</sub> = V<sub>GSB</sub> = 0 V. Both NMOS transistors (N<sub>A</sub>, N<sub>B</sub>) are in ON state Since its V<sub>GSA</sub> and V<sub>GSB</sub> is large positive (+5V). So NMOS transistors presents only a small resistance between Output and ground. Hence output is 0 V.

**Case (iii):** When A=0 V and B=5 V, then NMOS transistor (NA) is in OFF state, since its input voltage V<sub>GSA</sub>= 0 V and NMOS transistor (NB) is in ON state since its V<sub>GSB</sub>=5V. PMOS transistor (PA) is in ON state, since its V<sub>GSA</sub>= -5V and PMOS transistor (PB) is in OFF state since its V<sub>GSB</sub>=0V. So PMOS transistor PA presents only a small resistance between V<sub>DD</sub> and output. Hence output is 5 V.

**Case (iv):** When A=5 V and B=0 V, then NMOS transistor (NA) is in ON state, since its input voltage V<sub>GSA</sub>= +5V and NMOS transistor (NB) is in OFF state since its V<sub>GSB</sub>=0V. PMOS transistor (PA) is in OFF state, since its V<sub>GSA</sub>= 0V and PMOS transistor (PB) is in ON state since its V<sub>GSB</sub>=-5V. So PMOS transistor PB presents only a small resistance between V<sub>DD</sub> and output. Hence output is 5 V.

Fig: Two Input NOR gate circuit using CMOS logic

**NOTE:** For a given Si Area N-Channel Transistor has lower ON resistance than P-Channel Transistor. So, the circuit having series N-Channel connection is more faster than Parallel PChannel, Hence NAND circuit is faster than NOR.

Transistor-Transistor Logic Families are classified as following:

- (a) Early TTL families

- 74L Low power

- 74H High speed

- (b) Schottky TTL families

- 74S Schottky

- 74LS Low power Schottky

- 74AS Advanced Schottky

- 74ALS Advanced Low power Schottky

- 74F Fast

#### (a) Early TTL families:

- ➤ The original TTL family of logic gates was introduced by Sylvania in 1963. It was popularized by Texas Instruments, whose "7400-series" part numbers for gates and other TTL components quickly became an industry standard.

- ➤ As in 7400-series CMOS, devices in a given TTL family have part numbers of the form 74FAMnn, where "FAM" is an alphabetic family mnemonic and nn is a numeric function designator. Devices in different families with the same value of nn perform the same function.

In the original TTL family, "FAM" is null and the family is called 74-series TTL.

- The 74H (High speed TTL) family used lower resistor values to reduce propagation delay at the expense of increased power consumption.

- ➤ The 74L (Low-power TTL) family used higher resistor values to reduce power consumption at the expense of propagation delay.

## (b) Schottky TTL families:

➤ The first family to make use of Schottky transistors was 74S (Schottky TTL). With Schottky

transistors and low resistor values, this family has much higher speed, but higher power consumption, than the original 74-series TTL.

- > 74LS (Low-power Schottky TTL), introduced shortly after 74S. By combining Schottky transistors with higher resistor values, 74LS TTL matches the speed of 74- series TTL but has about one-fifth of its power consumption.

- ➤ Thus, 74LS is a preferred logic family for new TTL designs. Subsequent IC processing and circuit innovations gave rise to two more Schottky logic families as 74AS (Advanced Schottky TTL) and 74ALS (Advanced Low-power Schottky TTL).

- ➤ The 74AS (Advanced Schottky TTL) family offers speeds approximately twice as fast as 74S with approximately the same power consumption.

- ➤ The 74ALS (Advanced Low-power Schottky TTL) family offers both lower power and higher speeds than 74LS, and rivals 74LS in popularity for general-purpose requirements in new TTL designs.

- The 74F (Fast TTL) family is positioned between 74AS and 74ALS in the speed/power tradeoff, and is probably the most popular choice for high-speed requirements in new TTL designs.

## Characteristics of TTL logic families:

- The important characteristics of TTL families are summarized in Table 4.17.

- The first two rows of the table list the propagation delay (in nanoseconds) and the power consumption (in milliWatts) of a typical 2-input NAND gate in each family.

- ➤ One figure of merit of a logic family is its *speed-power product* listed in the third row of the table.

- > The remaining rows have values of voltage levels for all TTL families.

|                             | 74  | 74S | 74LS | 74AS | 74ALS | 74F |

|-----------------------------|-----|-----|------|------|-------|-----|

| Performance ratings         |     |     |      |      |       |     |

| Propagation delay (ns)      | 9   | 3   | 9.5  | 1.7  | 4     | 3   |

| Power dissipation (mW)      | 10  | 20  | 2    | 8    | 1.2   | 6   |

| Max. clock rate (MHz)       | 35  | 125 | 45   | 200  | 70    | 100 |

| Fan-out (same series)       | 10  | 20  | 20   | 40   | 20    | 33  |

| Speed-Power product(pj)     | 90  | 60  | 19   | 13.6 | 4.8   | 18  |

| Voltage parameters          |     |     |      |      |       |     |

| V <sub>OH</sub> (min) (V)   | 2.4 | 2.7 | 2.7  | 2.5  | 2.5   | 2.5 |

| $V_{OL}(max)$ (V)           | 0.4 | 0.5 | 0.5  | 0.5  | 0.5   | 0.5 |

| $V_{\rm IH}({\rm min})$ (V) | 2.0 | 2.0 | 2.0  | 2.0  | 2.0   | 2.0 |

| $V_{ii}$ (max) (V)          | 0.8 | 0.8 | 0.8  | 0.8  | 0.8   | 0.8 |

Characteristics of TTL logic families.

different electrical characteristics.

- ➤ If two circuits that are going to interface have different Electrical characteristics, then direct contact can't be made.

- ➤ In such cases Driver and Load circuits are connected through INTERFACE. Interface circuitry shifts levels of voltage & current for compatibility.

- > Driver output signal must satisfy the requirements of load circuit.

- ➤ If both driver and load require different power supplies, then outputs of both circuits must swing between its specified voltage ranges

- The interfacing may done in between two different logic families or with in the same logic families.

- > Interfacing in between CMOS and TTL logic families is achieved in ways as

- (a) TTL Driving CMOS circuits.

- (b) CMOS driving TTL circuits.

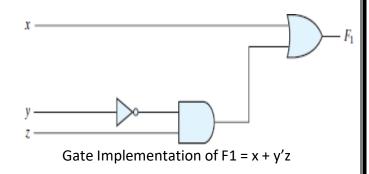

**Boolean Function**

Boolean algebra is an algebra that deals with binary variables and logic operations.

A Boolean function described by an algebraic expression consists of binary variables, the constants 0 and 1, and the logic operation symbols.

For a given value of the binary variables, the function can be equal to either 1 or 0.

Consider an example for the Boolean function

$$F1 = x + y'z$$

The function F1 is equal to 1 if x is equal to 1 or if both y' and z are equal to 1. F1 is equal to 0 otherwise. The complement operation dictates that when y' = 1, y = 0. Therefore, F1 = 1 if x = 1 or if y = 0 and z = 1.

A Boolean function expresses the logical relationship between binary variables and is evaluated by determining the binary value of the expression for all possible values of the variables.

A Boolean function can be represented in a truth table. The number of rows in the truth table is  $2^n$ , where n is the number of variables in the function. The binary combinations for the truth table are obtained from the binary numbers by counting from 0 through  $2^n - 1$ .

# ENGINEERING COLLEGE

## Truth Table for F1

| Х | У | Z | F <sub>1</sub> |

|---|---|---|----------------|

| 0 | 0 | 0 | 0              |

|   |   |   |                |

0 | 0 | 1

#### Note:

Q: Let a function F() depend on n variables. How many rows are there in the truth table of F()? A: 2<sup>n</sup> rows, since there are 2<sup>n</sup> possible binary patterns/combinations for the n variables.

vour robis lo success...

NARSIMHA REDDY ENGINEERING COLLEGE

#### **Truth Tables**

- Enumerates all possible combinations of variable values and the corresponding function value

- Truth tables for some arbitrary functions F1(x,y,z), F2(x,y,z), and F3(x,y,z) are shown to the below.

| х | У | Z | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> |

|---|---|---|----------------|----------------|----------------|

| 0 | 0 | 0 | 0              | 1              | 1              |

| 0 | 0 | 1 | 0              | 0              | 1              |

| 0 | 1 | 0 | 0              | 0              | 1              |

| 0 | 1 | 1 | 0              | 1              | 1              |

| 1 | 0 | 0 | 0              | 1              | 0              |

| 1 | 0 | 1 | 0              | 1              | 0              |

| 1 | 1 | 0 | 0              | 0              | 0              |

| 1 | 1 | 1 | 1              | 0              | 1              |

- Truth table: a <u>unique</u> representation of a Boolean function

- If two functions have identical truth tables, the functions are equivalent (and viceversa).

- Truth tables can be used to prove equality theorems.

- However, the size of a truth table grows <u>exponentially</u> with the number of variables involved, hence unwieldy. This motivates the use of Boolean Algebra.

## **Boolean expressions-NOT unique**

Unlike truth tables, expressions epresenting a Boolean function are NOT unique.

- Example:

- $F(x,y,z) = x' \cdot y' \cdot z' + x' \cdot y \cdot z' + x \cdot y \cdot z' + x \cdot y \cdot z'$

- $G(x,y,z) = x' \bullet y' \bullet z' + y \bullet z'$

- The corresponding truth tables for

F() and G() are to the right. They are identical.

- Thus, F() = G()

| Х | У | Z | F | G |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

|   |   |   |   |   |

## Algebraic Manipulation (Minimization of Boolean function)

- Boolean algebra is a useful tool for simplifying digital circuits.

- Why do it? Simpler can mean cheaper, smaller, faster.

- Example: Simplify F = x'yz + x'yz' + xz.

$$F = x'yz + x'yz' + xz$$

$$= x'y(z+z') + xz$$

$$= x'y \cdot 1 + xz$$

$$= x'y + xz$$

Example: Prove

$$x'y'z' + x'yz' + xyz' = x'z' + yz'$$

• Proof:

$$x'y'z' + x'yz' + xyz'$$

=  $x'y'z' + x'yz' + x'yz' + xyz'$

=  $x'z'(y'+y) + yz'(x'+x)$

=  $x'z' \cdot 1 + yz' \cdot 1$

=  $x'z' + yz'$

## **Complement of a Function**

- The complement of a function is derived by interchanging (• and +), and (1 and 0), and complementing each variable.

- Otherwise, interchange 1s to 0s in the truth table column showing F.

- The complement of a function IS NOT THE SAME as the dual of a function.

#### Example

Find G(x,y,z), the complement of F(x,y,z) = xy'z' + x'yz

Ans: G = F' = (xy'z' + x'yz)'

= (xy'z')' • (x'yz)'

DeMorgan

= (x'+y+z) • (x+y'+z')

**Note:** The complement of a function can also be derived by finding the function's *dual*, and then complementing all of the literals

ENGINEERING COLLEGE

#### **Canonical and Standard Forms**

We need to consider formal techniques for the simplification of Boolean functions. Identical functions will have exactly the same canonical form.

- Minterms and Maxterms

- Sum-of-Minterms and Product-of- Maxterms

- Product and Sum terms

- Sum-of-Products (SOP) and Product-of-Sums (POS)

#### **Definitions**

**Literal:** A variable or its complement **Product term:** literals connected by • **Sum term:** literals connected by +

Minterm: a product term in which all the variables appear exactly once, either complemented or uncomplemented.

**Maxterm:** a sum term in which all the variables appear exactly once, either complemented or uncomplemented.

**Canonical form:** Boolean functions expressed as a sum of Minterms or product of Maxterms are said to be in canonical form.

#### Minterm

- Represents exactly one combination in the truth table.

- Denoted by m<sub>j</sub>, where j is the decimal equivalent of the minterm's corresponding binary combination (b<sub>i</sub>).

- A variable in m<sub>i</sub> is complemented if its value in b<sub>i</sub> is 0, otherwise is uncomplemented.

Example: Assume 3 variables (A, B, C), and j=3. Then,  $b_j$  = 011 and its corresponding minterm is denoted by  $m_j$  = A'BC

#### Maxterm

- Represents exactly one combination in the truth table.

- Denoted by  $M_j$ , where j is the decimal equivalent of the maxterm's corresponding binary combination  $(b_i)$ .

- A variable in  $M_j$  is complemented if its value in  $b_j$  is 1, otherwise is uncomplemented.

Example: Assume 3 variables (A, B, C), and j=3. Then,  $b_j=0.11$  and its corresponding maxterm is denoted by  $M_j=A+B'+C'$

## **Truth Table notation for Minterms and Maxterms**

Minterms and Maxterms are easy to denote using a truth table.

Example: Assume 3 variables x,y,z (order is fixed)

| Х | У | Z | Minterm                 | Maxterm                                |

|---|---|---|-------------------------|----------------------------------------|

| 0 | 0 | 0 | $x'y'z' = m_0$          | $x+y+z = M_0$                          |

| 0 | 0 | 1 | $x'y'z = m_1$           | $x+y+z' = M_1$                         |

| 0 | 1 | 0 | $x'yz' = m_2$           | $x+y'+z = M_2$                         |

| 0 | 1 | 1 | x'yz = m <sub>3</sub>   | x+y'+z'= M <sub>3</sub>                |

| 1 | 0 | 0 | xy'z' = m <sub>4</sub>  | $x' + y + z = M_4$                     |

| 1 | 0 | 1 | xy'z <mark>= m</mark> 5 | $x'+y+z' = M_5$                        |

| 1 | 1 | 0 | xyz' = m <sub>6</sub>   | x'+ <mark>y'+z =</mark> M <sub>6</sub> |

| 1 | 1 | 1 | xyz = m <sub>7</sub>    | $x'+y'+z'=M_7$                         |

#### **Canonical Forms**

- Every function F() has two canonical forms:

- Canonical Sum-Of-Products (sum of minterms)

- Canonical Product-Of-Sums (product of maxterms)

Canonical Sum-Of-Products:

The minterms included are those  $m_j$  such that F() = 1 in row j of the truth table for F().

Canonical Product-Of-Sums:

The maxterms included are those  $M_i$  such that F() = 0 in row j of the truth table for F().

## Example

Consider a Truth table for f<sub>1</sub>(a,b,c) at right

The canonical sum-of-products form for f<sub>1</sub> is

$$f_1(a,b,c) = m_1 + m_2 + m_4 + m_6$$

$$= a'b'c + a'bc' + ab'c' + abc'$$

The canonical product-of-sums form for f<sub>1</sub> is

$$f_1(a,b,c) = M_0 \bullet M_3 \bullet M_5 \bullet M_7$$

$$= (a+b+c) \bullet (a+b'+c') \bullet (a'+b+c') \bullet (a'+b'+c').$$

Observe that: m<sub>i</sub> = M<sub>i</sub>'

|   | а | b | С | $f_1$ |

|---|---|---|---|-------|

|   | 0 | 0 | 0 | 0     |

|   | 0 | 0 | 1 | 1     |

|   | 0 | 1 | 0 | 1     |

| Ĺ | 0 | 1 | 1 | 0     |

|   | 1 | 0 | 0 | 1     |

|   | 1 | 0 | 1 | 0     |

|   | 1 | 1 | 0 | 1     |

|   | 1 | 1 | 1 | 0     |

|   | • |   | • | •     |

## Shorthand: ∑ and ∏

- $f_1(a,b,c) = \sum m(1,2,4,6)$ , where  $\sum$  indicates that this is a sum-of-products form, and m(1,2,4,6) indicates that the minterms to be included are  $m_1$ ,  $m_2$ ,  $m_4$ , and  $m_6$ .

- $f_1(a,b,c) = \prod M(0,3,5,7)$ , where  $\prod$  indicates that this is a product-of-sums form, and M(0,3,5,7) indicates that the maxterms to be included are  $M_0$ ,  $M_3$ ,  $M_5$ , and  $M_7$ .

- Since  $m_j = M_j'$  for any j,  $\sum m(1,2,4,6) = \prod M(0,3,5,7) = f_1(a,b,c)$

#### **Conversion between Canonical Forms**

- Replace  $\Sigma$  with  $\prod$  (or *vice versa*) and replace those j's that appeared in the original form with those that do not.

- Example:

$$f_{1}(a,b,c) = a'b'c + a'bc' + ab'c' + abc'$$

$$= m_{1} + m_{2} + m_{4} + m_{6}$$

$$= \sum (1,2,4,6)$$

$$= \prod (0,3,5,7)$$

$$= (a+b+c) \cdot (a+b'+c') \cdot (a'+b+c') \cdot (a'+b'+c')$$

#### **Standard Forms**

Another way to express Boolean functions is in standard form. In this configuration, the terms that form the function may contain one, two, or any number of literals.

There are two types of standard forms: the sum of products and products of sums.

The sum of products is a Boolean expression containing AND terms, called product terms, with one or more literals each. The sum denotes the ORing of these terms. An example of a function expressed as a sum of products is

$$F1 = y' + xy + x'yz'$$

The expression has three product terms, with one, two, and three literals. Their sum is, in effect, an OR operation.

A product of sums is a Boolean expression containing OR terms, called sum terms. Each term may have any number of literals. The product denotes the ANDing of these terms. An example of a function expressed as a product of sums is

$$F2 = x(y' + z)(x' + y + z')$$

This expression has three sum terms, with one, two, and three literals. The product is an AND operation.

## Conversion of SOP from standard to canonical form

## Example-1.

Express the Boolean function F = A + B'C as a sum of minterms.

Solution: The function has three variables: A, B, and C. The first term A is missing two variables; therefore,

$$A = A(B + B') = AB + AB'$$

This function is still missing one variable, so

$$A = AB(C + C') + AB'(C + C')$$

$$= ABC + ABC' + AB'C + AB'C'$$

The second term B'C is missing one variable; hence,

$$B'C = B'C(A + A') = AB'C + A'B'C$$

Combining all terms, we have

$$F = A + B'C$$

$$= ABC + ABC' + AB'C + AB'C' + A'B'C$$

But AB'C appears twice, and according to theorem (x + x = x), it is possible to remove one of those occurrences. Rearranging the minterms in ascending order, we finally obtain

$$F = A'B'C + AB'C + AB'C + ABC' + ABC$$

$$= m1 + m4 + m5 + m6 + m7$$

When a Boolean function is in its sum-of-minterms form, it is sometimes convenient to express the function in the following brief notation:

$$F(A, B, C) = \sum m (1, 4, 5, 6, 7)$$

#### Example-2.

Express the Boolean function F = xy + x'z as a product of maxterms.

Solution: First, convert the function into OR terms by using the distributive law:

$$F = xy + x'z = (xy + x')(xy + z)$$

$$= (x + x')(y + x')(x + z)(y + z)$$

$$= (x'+y)(x+z)(y+z)$$

13 13 13 13 15 10 13 15

The function has three variables: x, y, and z. Each OR term is missing one variable; therefore,

$$x'+y=x'+y+zz'=(x'+y+z)(x'+y+z')$$

$$x + z = x + z + yy' = (x + y + z)(x + y' + z)$$

$$y + z = y + z + xx' = (x + y + z)(x' + y + z)$$

Combining all the terms and removing those which appear more than once, we finally obtain

$$F = (x + y + z)(x + y' + z)(x' + y + z)(x' + y + z)$$

A convenient way to express this function is as follows:

$$F(x, y, z) = \pi M(0, 2, 4, 5)$$

The product symbol,  $\pi$ , denotes the ANDing of maxterms; the numbers are the indices of the maxterms of the function.

## **Digital Logic Gates**

Boolean functions are expressed in terms of AND, OR, and NOT operations, it is easier to implement a Boolean function with these type of gates.

| Name                               | Graphic<br>symbol | Algebraic<br>function           | Truth<br>table                            |        |

|------------------------------------|-------------------|---------------------------------|-------------------------------------------|--------|

| AND                                | <i>x</i>          | $F = x \cdot y$                 | x y F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1 | -      |

| OR                                 | <i>x</i>          | F - x + y                       | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1 | -      |

| Inverter                           | x                 | F = x'                          | x F<br>0 1<br>1 0                         | -      |

| Buffer                             | xF                | F = x                           | x F<br>0 0<br>1 1                         | F      |

| NAND                               | х<br>у            | F= (xy)'                        | x y F<br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0 |        |

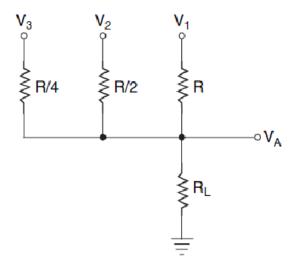

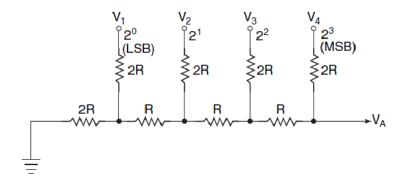

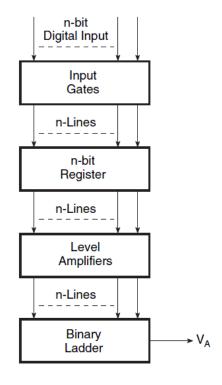

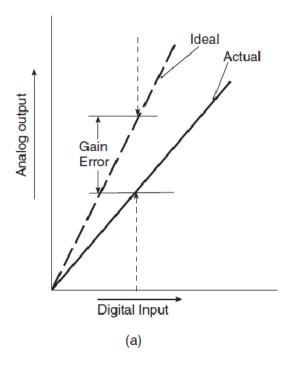

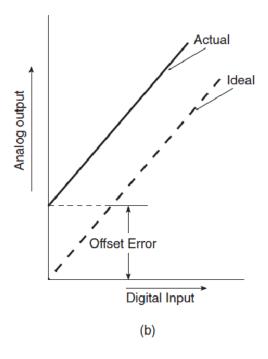

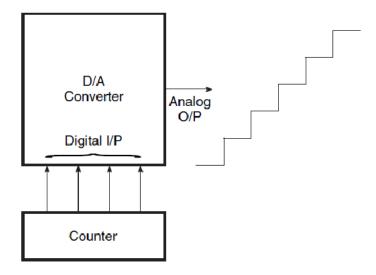

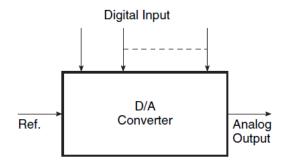

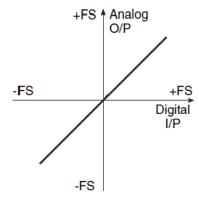

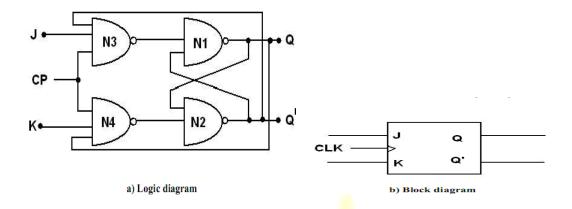

| NOR                                | x                 | F = (x + y)'                    | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0 | l.     |